# Integrated Module Heat Exchanger

Kevin Bennion National Renewable Energy Laboratory May 15, 2012

Project ID #: APE047

This presentation does not contain any proprietary, confidential, or otherwise restricted information.

NREL is a national laboratory of the U.S. Department of Energy, Office of Energy Efficiency and Renewable Energy, operated by the Alliance for Sustainable Energy, LLC.

### **Overview**

#### Timeline

Project Start Date: FY 2012 Project End Date: FY 2013 Percent Complete: 30%

#### **Budget**

**Total Project Funding:** DOE Share:\$200K (FY12)

#### Funding Received in FY11: \$0K

Funding for FY12: \$200K

#### **Barriers and Targets**

• Cost

Performance (Power Density)

#### **Partners**

- Interactions / collaborations

- Sapa

- Project lead

- National Renewable Energy Laboratory

# **Relevance/Objectives**

#### Problem: Cost, Volume, and Weight

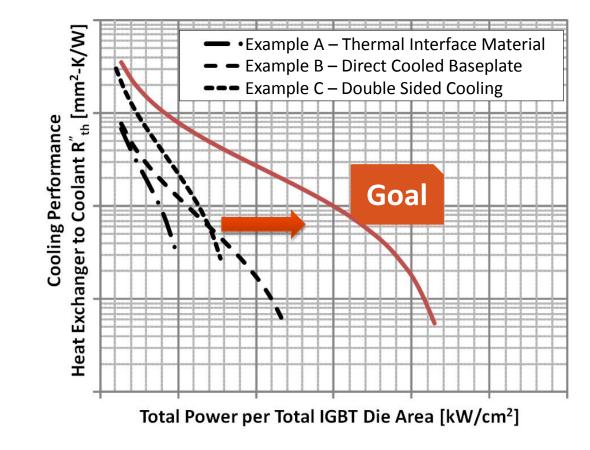

"Easy ways to increase output power are paralleling more silicon chips and/or step-up the die size to increase current capacity. But this strategy is unaffordable in terms of both increased chip cost and packaging space." (2007)<sup>[1]</sup>

# Primary Concern: Heat "The most significant concern for increasing current is intensified heat dissipation in the silicon chips" (2007) <sup>[1]</sup>

Total Power per Total IGBT Die Area [kW/cm<sup>2</sup>]

[1] Source: Yasui, H., et al., "Power Control Unit of High Power Hybrid System" – Denso and Toyota, SAE 2007-01-0271

# **Relevance/Objectives**

#### Problem: Cost, Volume, and Weight

"Easy ways to increase output power are paralleling more silicon chips and/or step-up the die size to increase current capacity. But this strategy is unaffordable in terms of both increased chip cost and packaging space." (2007)<sup>[1]</sup>

#### Primary Concern: Heat

"The most significant concern for increasing current is intensified heat dissipation in the silicon chips" (2007)<sup>[1]</sup>

#### Current Technology:

Packaging and cooling developments have improved heat removal to increase power capability (power per die area)

#### Goal:

Improve heat dissipation to improve power per die area (cost)

[1] Source: Yasui, H., et al., "Power Control Unit of High Power Hybrid System" – Denso and Toyota, SAE 2007-01-0271

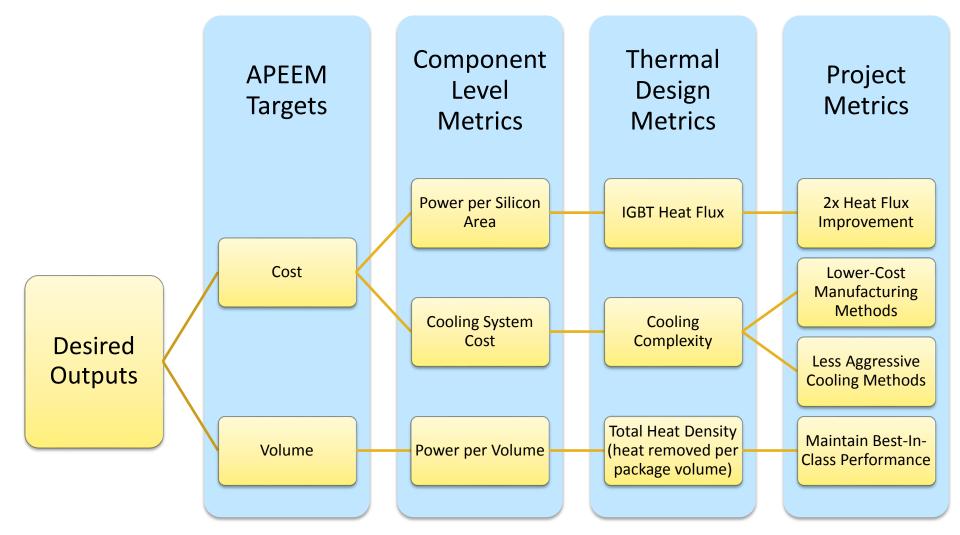

### **Relevance/Objectives**

#### **Objective**

• Design and build a prototype heat exchanger module that improves power per die area capability while enabling low cost and scalable heat exchanger technologies

#### **Addresses Targets**

- Reduces cost by:

- Improving the power per die area by 100%

- Introducing a modular and scalable thermal approach to reduce the need for custom heat exchanger redesigns as applications scale in power

- Reduces weight by eliminating large heat exchanger cold plates

- Maintains best-in-class power density capabilities

#### **Uniqueness and Impacts**

- Technology is scalable to liquid-cooled systems and air-cooled systems

- Research will improve liquid and air cooling of power electronics

[1] Credit: Mark Mihalic, NREL

[2] Credit: Kevin Bennion, NREL

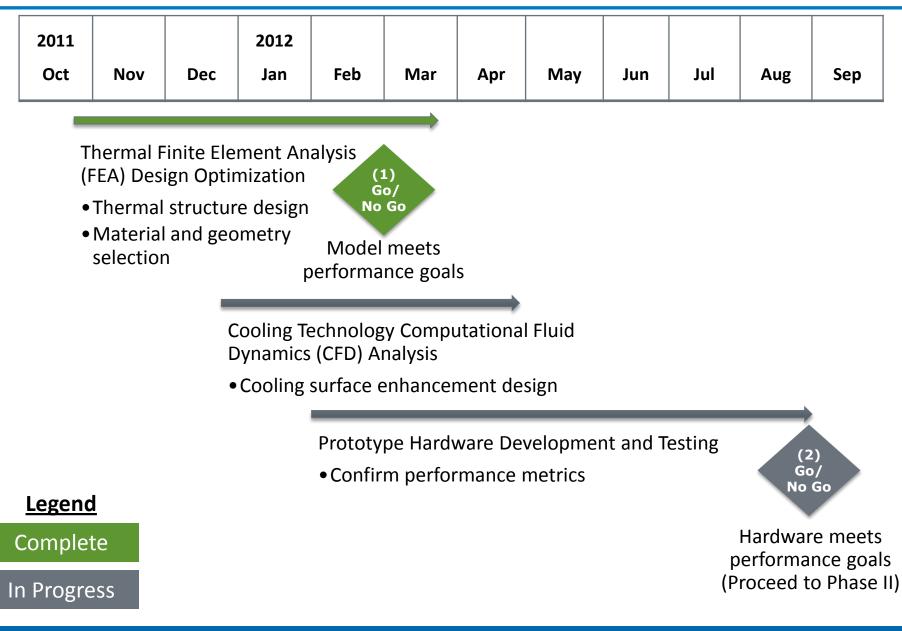

### **Milestones**

| Date           | Milestone or Go/No-Go Decision                                                                                                                                                           |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2011 | Internal Milestone:<br>• Patent application submitted                                                                                                                                    |

| February 2012  | Go/No-Go:<br>• Computer simulations of design match preliminary analysis<br>expectations and justify hardware prototype development                                                      |

| April 2012     | Internal Milestone:<br>• Finalize initial prototype design                                                                                                                               |

| September 2012 | <ul><li>DOE Milestone:</li><li>Complete hardware tests on prototype</li><li>Submit report on design and test results</li></ul>                                                           |

|                | <ul> <li>Go/No-Go:</li> <li>Prototype heat exchanger hardware matches design expectation</li> <li>Proceed to second project phase to integrate with power electronics package</li> </ul> |

APEEM – Advanced Power Electronics and Electric Motors IGBT – Insulated Gate Bipolar Transistor

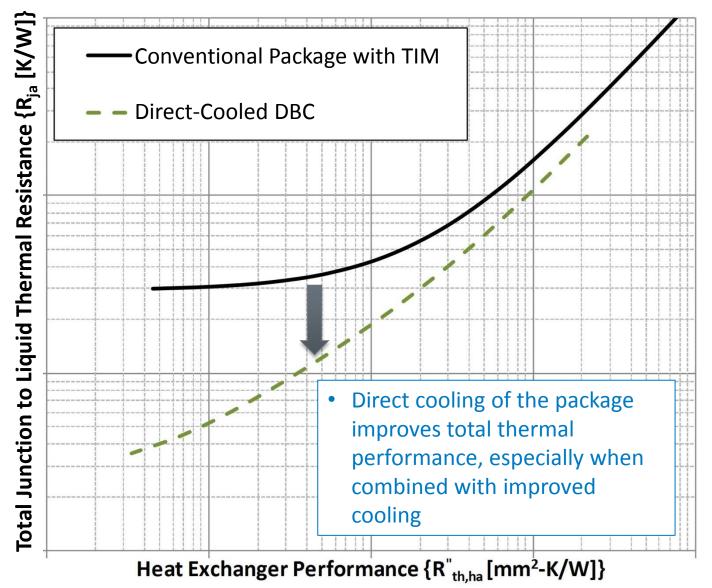

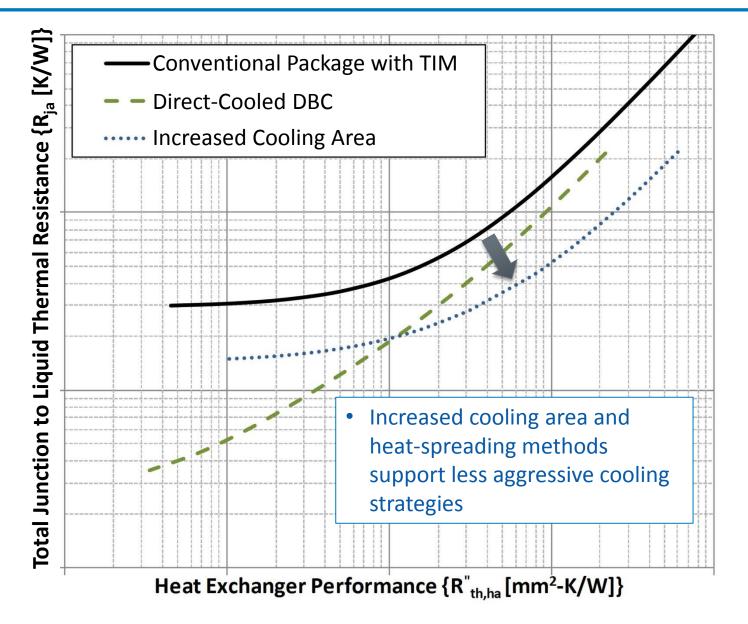

TIM: Thermal Interface Material

DBC: Direct Bond Copper

K. Bennion and K. Kelly, *Rapid Modeling of Power Electronics Thermal Management Technologies*, NREL Milestone Report, Jul. 2009.

T. Burress, C. Coomer, S. Campbell, A. Wereszczak, J. Cunningham, L. Marlino, L. Seiber, and H.-T. Lin, *Evaluation of the 2008 Lexus LS 600H Hybrid Synergy Drive System*. Oak Ridge National Laboratory. ORNL/TM-2008/185, Jan. 2009.

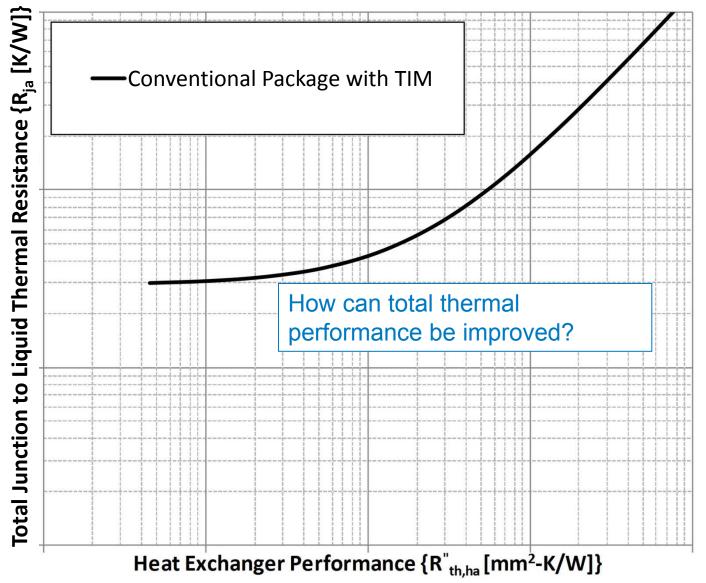

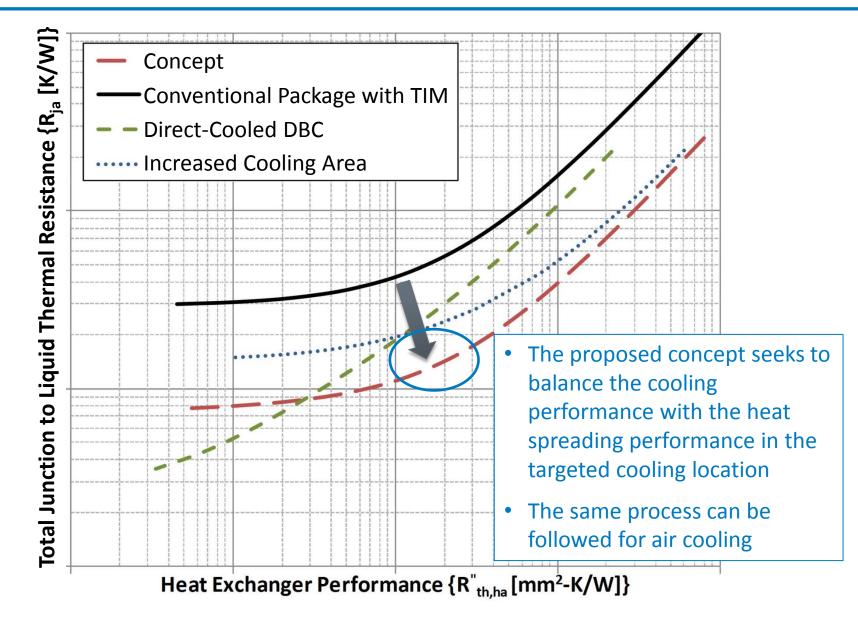

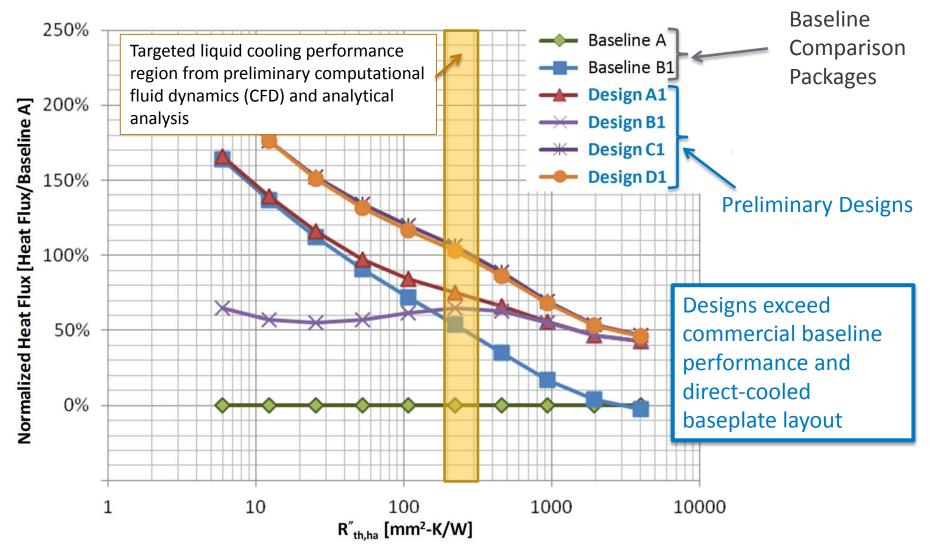

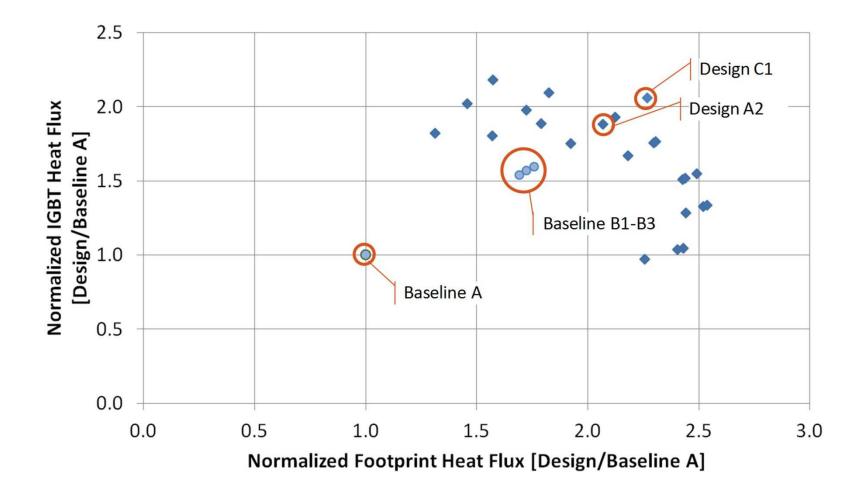

#### Compared performance of alternative designs at targeted cooling performance region

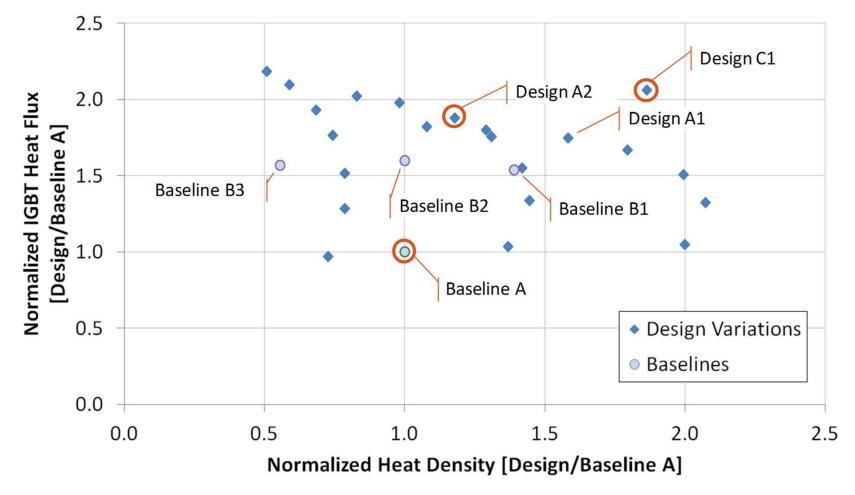

#### Compared designs relative to baseline packages (heat density versus IGBT heat flux)

- Design C1 shows best performance but has cost concerns

- Design A2 shows good performance across design goals

Heat Density = Heat Rejection/Package Volume

Compared designs relative to baseline packages (footprint heat flux versus IGBT heat flux)

Footprint Heat Flux = Heat Rejection/Base Footprint Area

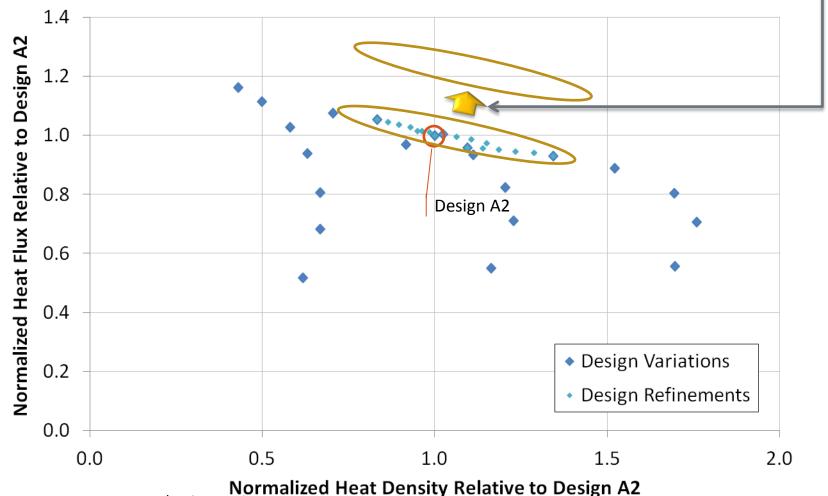

Performed parametric design study around the selected design point (Design A2)

• A significant jump to a better operating region was not found within the design constraints

• Proceeding with Design A2

Heat Density = Heat Rejection/Package Volume

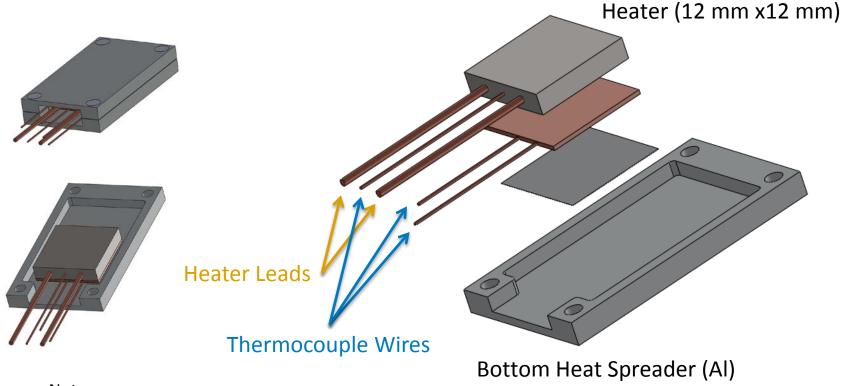

# Developing heater package to represent power semiconductor package for prototype testing

- Capable of single- or double-sided cooling

- Enables validation of thermal model

- Represents generic power semiconductor package

#### Note:

- Preliminary design

- Additional thermocouples will be placed on the heat spreader plate, which is not shown.

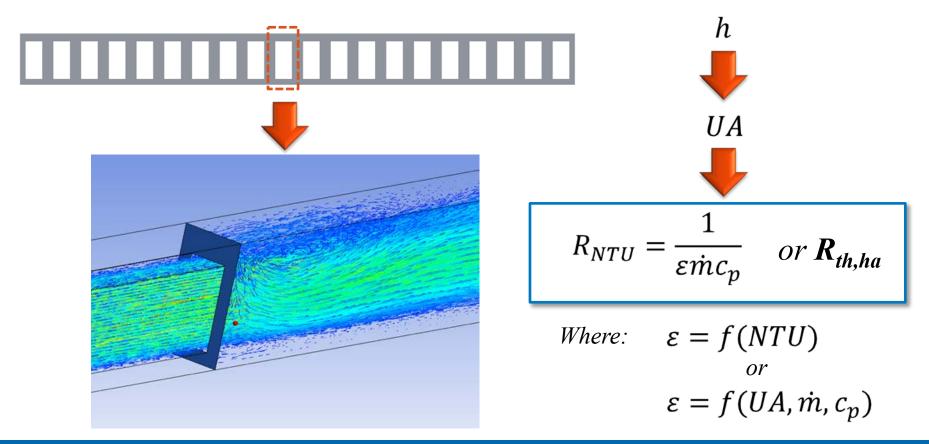

#### Developing CFD model for heat transfer design

- Provided preliminary estimate for heat exchanger cooling performance

- Compared against analytical methods

- Focusing initially on channel flow

- Moving towards more complex, full-system CFD for additional design studies and fin design

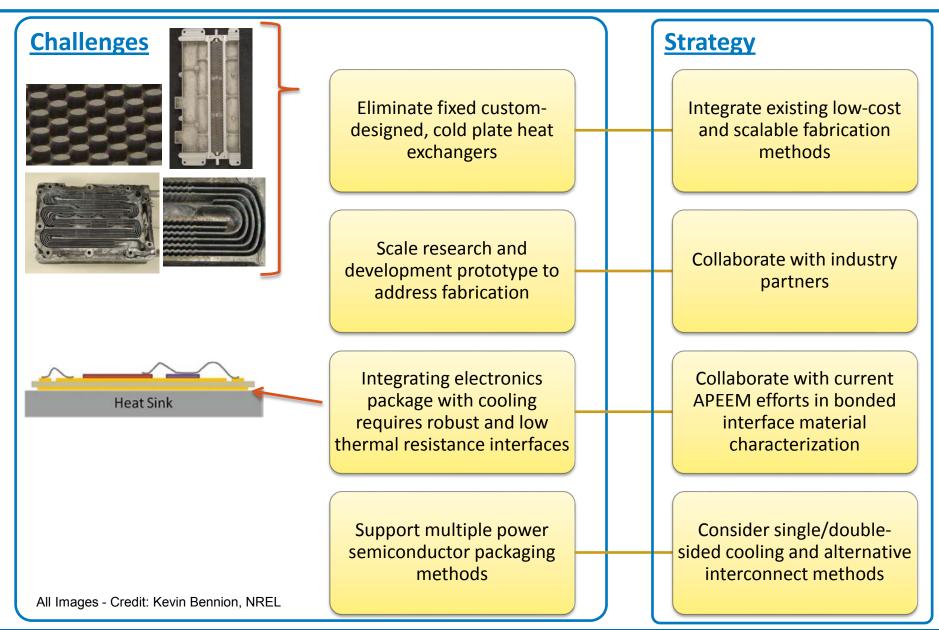

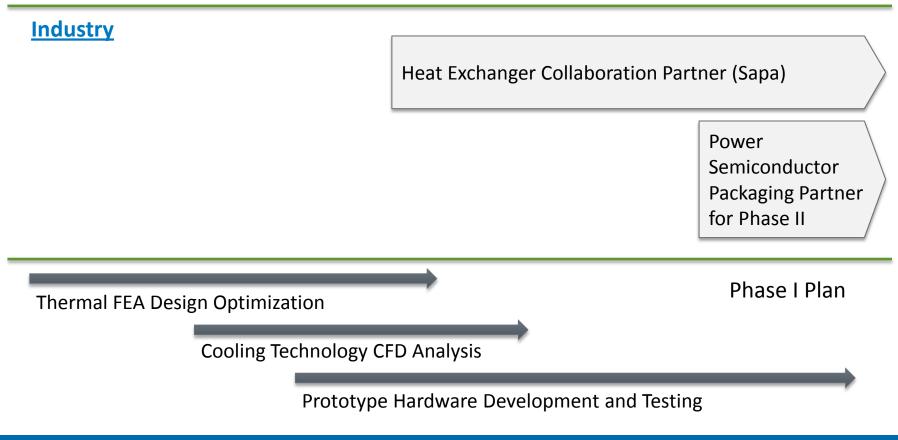

# **Collaboration and Coordination**

#### **Other Government Laboratories**

Oak Ridge National Laboratory/APEEM Program

- Support from benchmarking activities

- Ensure thermal design space is appropriate and modeling assumptions are consistent with other aspects of APEEM research

### **Proposed Future Work**

#### FY12 (Phase I)

- Software Prototype Design

- Refine prototype heat exchanger design through full-system CFD thermal and fluid analysis

- Hardware Prototype Testing

- Build prototype of heat exchanger module with heat sources representing power electronics package

- Compare experimental results against model results

- Go/No-Go: If prototype heat exchanger hardware matches design expectation, proceed to second project phase to refine design and integrate with a power electronics package.

### **Proposed Future Work**

If FY12 simulation and test results achieve design targets, the plan is to proceed to the second project phase in FY13

#### • FY13 (Phase II)

- Incorporate lessons learned from Phase I prototype build to refine design to improve performance and fabrication

- Identify partner for power electronics package

- Design and build second prototype heat exchanger module integrated with power electronics package

- Complete testing of integrated heat exchanger module

- Explore opportunity for application to air cooling

### **Summary**

#### Relevance

- Increased heat dissipation is necessary to reduce power semiconductor cost, weight, and volume

- Integration of the power electronics package thermal design and the cooling design can improve power semiconductor performance

- A modular and scalable thermal approach can reduce the need for custom heat exchanger redesigns as applications scale in power

### **Approach/Strategy**

- Optimize integrated thermal package design and cooling technology for the targeted cooling performance

- Reduce cost by increasing semiconductor heat flux

- Reduce cost by enabling less aggressive and lower cost cooling methods

- Maintain best-in-class power density while doubling semiconductor heat flux

- Enable compatibility to alternative power semiconductor packaging technologies

### **Summary**

#### **Technical Accomplishments**

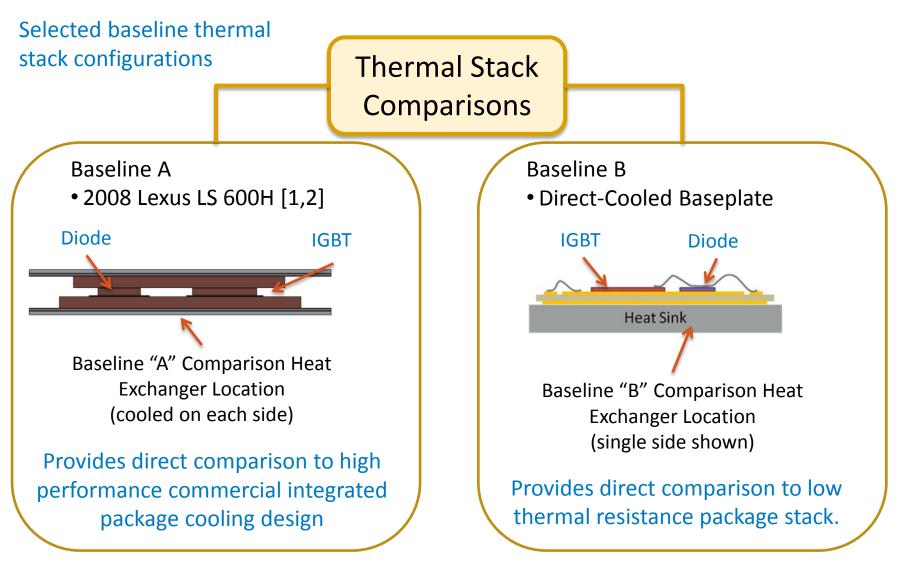

- Selected and analyzed baseline thermal stack configurations for performance benchmarking

- Compared performance of alternative designs at targeted cooling performance region against selected baseline configurations

- Performed parametric design study around the selected design point and selected preliminary design for hardware prototype testing

- Developing heater package to represent power semiconductor package for prototype testing

- Developing CFD model for heat transfer design

### **Collaborations**

- Established collaboration with heat exchanger development partner (Sapa)

- Future work will look to incorporate power semiconductor partner as project transitions to Phase II

#### **Acknowledgments:**

Susan Rogers and Steven Boyd, U.S. Department of Energy

#### **Team Members:**

Justin Cousineau Jason Lustbader

#### For more information contact:

Principal Investigator Kevin Bennion Kevin.Bennion@nrel.gov Phone: (303)-275-4447

#### **APEEM Task Leader:**

Sreekant Narumanchi Sreekant.Narumanchi@nrel.gov Phone: (303)-275-4062